2.在嵌入式系统设计中,李工使用某嵌入式处理器和对应的以太网芯进行带有网络功能的单板实现,该电路中还包含DDR、Flash等存储芯片和相应的外围控制芯片。

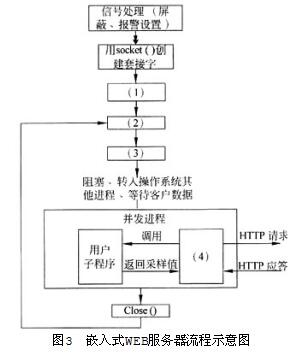

图1为所选用嵌入式处理器的存储模块存储地址总线变换示意图,

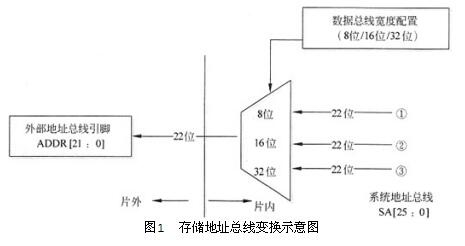

图2为以太网芯片外围设计的相关原理示意图,

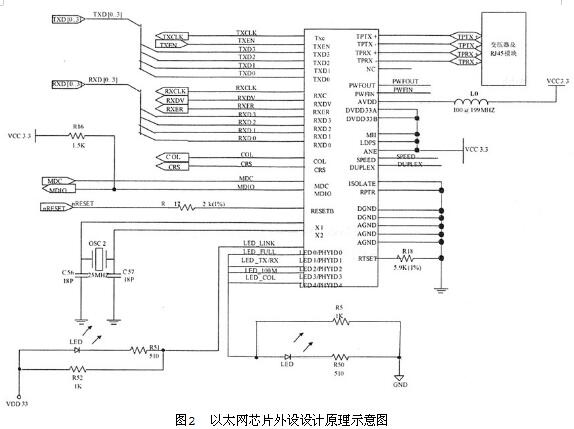

图3为用户在该嵌入式单板系统上实现内部嵌入式Web服务器的流程示意图。

在该嵌入式处理器的存储系统设计中,嵌入式处理器内部包含SA[25:0](从高到低)共26根系统地址总线,外部使用22根数据线和外部存储设备进行连接。 嵌入式处理器和以太网芯片之间的交互接口为:MII(Media Independent Interface)接口,包含数据线和控制线。数据线分为收发两个方向:其中RXD[3:0]为并行数据接收线,RXCLK为对应的时钟线;TXD[3:0]为并行数据发送线,TXCLK为对应的时钟线。

MDIO和MDC为控制线,通过其进行以太网芯片的配置。以太网芯片的最大通信频率由其外围的晶振频率和收发数据线的并行数目决定。 在嵌入式系统设计中,嵌入式处理器和以太网芯片之间可以设计为一对多的方式,每个以太网控制器都有一个PHYID,该PHYID依赖于以太网芯片周边的电路设计。在图2的设计中,该以太网芯片的PHYID由图中的PHYID[4:0]五个管脚来定。

对于该以太网芯片而言,PHYID[4:0]在启动时是作为。PHYID选择控制使用,在启动后是作为其他指示功能使用。PHYID的最大值是31(五位),最小是0,由PHYID[4:0]从高位到低位决定,对应管脚为高电平时对应的值为1,低电平时对应的值为0。

1、如图1所示,用户可以通过寄存器将存储总线变换方式配置为字节模式(8位模式),半字模式(16位模式)或者字模式(32位模式)中的任何一种,不同模式下,所使用到的地址线不同。 在图2中的,①、②、和③分别对应的地址线连接应该依次是______。 A SA2-SA23, SA1-SA22, SA0-SA21 B SA0-SA21, SA2-SA23, SA1-SA22 C SA1-SA22, SA2-SA23, SA0-SA21 D SA0-SA21, SA1-SA22, SA2-SA23 根据图2的网络部分相关电路设计,可以知道该嵌入式处理器的网络通信中,最大通信频率是______Mbps。 A.10000 B.1000 C.100 D.10 如果该网络芯片工作在100Mbps,那么在图2的设计中,RXCLK的工作频率应该是______Mbps.根据图2的电路和题目说明,在该电路中,以太网芯片的PHYID应该是______。

2、在图3中,为了实现嵌入式Web服务器和对应的请求流程,李工设计了该流程示意图,根据网络通信的过程,从下面选项中选择合适的处理过程,填充图3中的空(1)~(4)。 空(1)~(4)备选答案: A.创建TCP socket套接字 B.关闭socket套接字 C.accept尝试建立TCP连接 D.HTTP服务 E.数据发送处理 F.数据接收处理 G.bind绑定套接字 H.本地其他服务处理 I.listen侦听客户套接字 J.创建UDP socket套接字