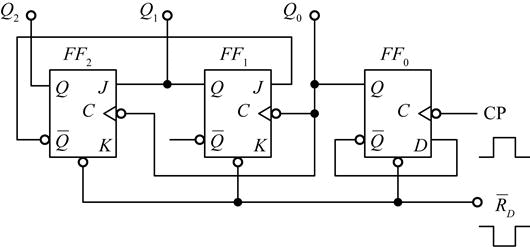

如图所示异步时序电路,该电路的逻辑功能( )。

- A.同步八进制加法计数器

- B.异步八进制减法计数器

- C.异步六进制加法计数器

- D.异步六进制减法计数器

正确答案及解析

正确答案

C

解析

每两个CP,D触发器才会使输出由0变为1给两个JK触发器一个上升沿。即D触发器动作两次,JK触发器动作一次(即Q1为1时)。K值永远为1,设立初始状态Q2Q1Q0为001,J1为1,J2为0,则当JK触发器触发,J1为1,Q1取反为1,J2为0,Q2与J2相同为0,此时Q2Q1Q0为011;这时J1为1,J2为1,则当JK触发器触发,J1为1,Q1取反为0,J2为1,Q2取反为1,此时Q2Q1Q0为101;这时J1为0,J2为0,则当JK触发器触发,J1为0,Q1与J1相同为0,J2为0,Q2与J2相同为0,此时Q2Q1Q0为001,此时开始下一轮的循环,即三次JK触发器触动为一个循环,所以3×2=6即为异步六进制加法计数器。