以下关于嵌入式系统时钟管理叙述中,错误是( )。

- A.系统主时钟可以由外部时钟源提供,也可由外部晶体振荡器提供

- B.时钟控制逻辑可以在不需要锁相环情况下产生慢速时钟

- C.利用锁相环可以对输入时钟进行倍频输出,但无法改变输出时钟相位

- D.可以通过软件来控制时钟与每个外围模块连接还是断开

正确答案及解析

正确答案

C

解析

系统主时钟可以由外部时钟源提供,也可由外部晶体振荡器提供。时钟控制逻辑可以在不需要锁相环情况下产生慢速时钟,并且可以通过软件来控制时钟与每个外围模块连接还是断开,从而降低功效。系统时钟源直接采用外部晶振时,内部PLL电路可以调整系统时钟,使系统运行速度更快。由于片内PPL电路可以兼具频率放大和信号提纯功能,因此,系统可以以较低外部时钟信号获得较高工作频率,从而降低因高速开关时钟所造成高频噪声。锁相环在工作过程中,当输出信号频率与输入信号频率相等时,输出电压与输入电压保持固定相位差值,即输出电压与输入电压相位被锁住。

你可能感兴趣的试题

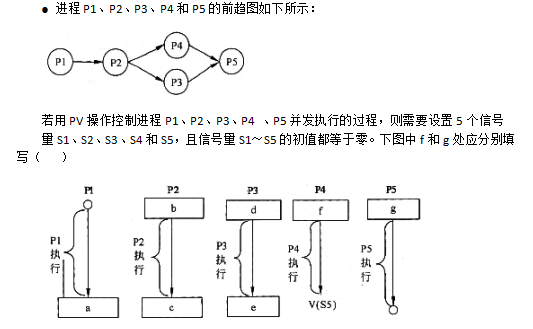

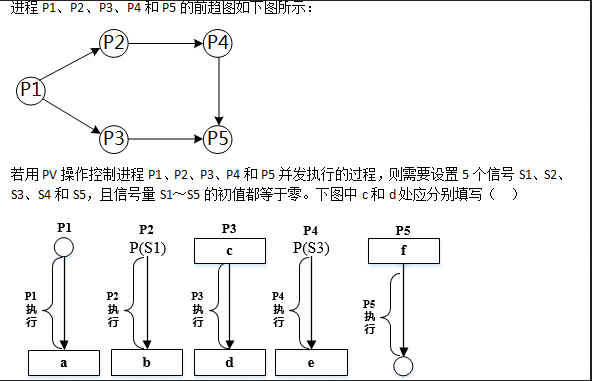

-

- A.V(S2)和P(S4)

- B.P(S2)和V(S4)

- C.P(S2)和P(S4)

- D.V(S2)和V(S4)

- 查看答案

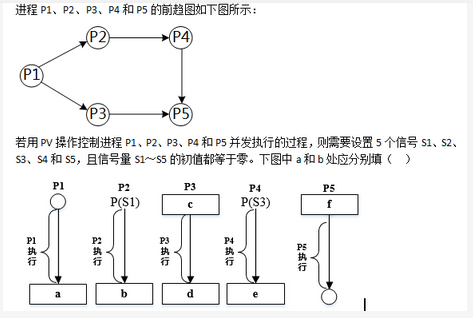

-

- A.V(S1)P(S2)和V(S3)

- B.P(S1)V(S2)和V(S3)

- C.V(S1)V(S2)和V(S3)

- D.P(S1)P(S2)和V(S3)

- 查看答案

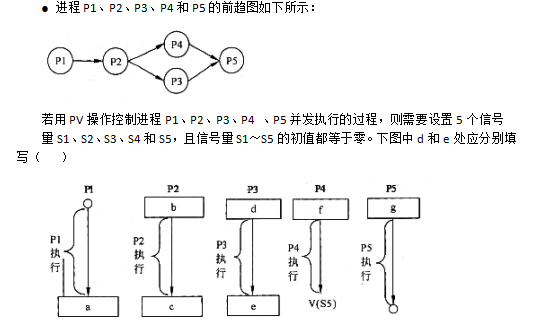

-

- A.P(S4)和V(S4)V(S5)

- B.V(S5)和P(S4)P(S5)

- C.V(S3)和V(S4)V(S5)

- D.P(S3)和P(S4)V(P5)

- 查看答案

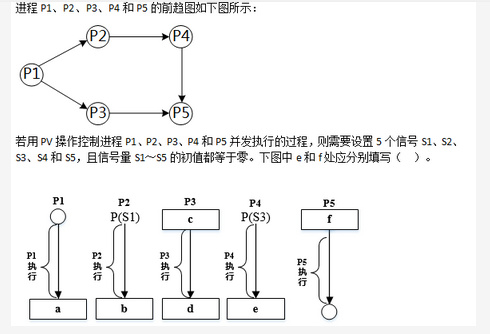

-

- A.P(S3)和V(S4)V(S5)

- B.V(S3)和P(S4)P(S5)

- C.P(S3)和P(S4)P(S5)

- D.V(S3)和V(S4)V(S5)

- 查看答案

-

- A.P(S2)和P(S4)

- B.P(S2)和V(S4)

- C.V(S2)和P(S4)

- D.V(S2)和V(S4)

- 查看答案