在主存储器和CPU之间增加Cache目是______。

- A.解决CPU和主存之间速度匹配问题

- B.扩大主存储器容量

- C.扩大CPU中通用寄存器数量

- D.既扩大主存储器容量,又扩大CPU中通用寄存器数量

正确答案及解析

正确答案

A

解析

本题考查计算机体系结构方面基础知识。高速缓冲存储器(Cache)是存在于主存与CPU之间一级存储器,由静态存储芯片(SRAM)组成,容量比较小但速度比主存高得多,接近于CPU速度。它和主存储器一起构成一级存储器。高速缓冲存储器和主存储器之间信息调度和传送是由硬件自动进行。在计算机技术发展过程中,主存储器存取速度一直比中央处理器操作速度慢得多,使中央处理器高速处理能力不能充分发挥,整个系统工作效率受到影响。有很多方法可用来缓和中央处理器和主存储器之间速度不匹配矛盾,如采用多个通用寄存器、多存储体交叉存取等,在存储层次上采用高速缓冲存储器也是常用方法之一。很多大、中型计算机以及新近一些小型机、微型机也都采用高速缓冲存储器。根据程序局部性原理,正在使用主存储器某一单元邻近那些单元将被用到可能性很大。因而,当中央处理器存取主存储器某一单元时,计算机硬件就自动地将包括该单元在内那一组单元内容调入高速缓冲存储器,中央处理器即将存取主存储器单元很可能就在刚刚调入到高速缓冲存储器那一组单元内。于是,中央处理器就可以直接对高速缓冲存储器进行存取。在整个处理过程中,如果中央处理器绝大多数存取主存储器操作能为存取高速缓冲存储器所代替,计算机系统处理速度就能显著提高。

你可能感兴趣的试题

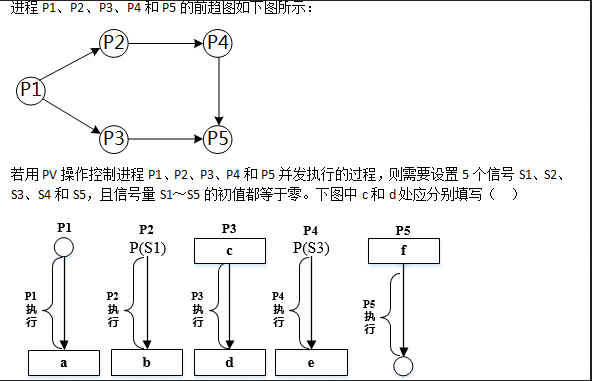

-

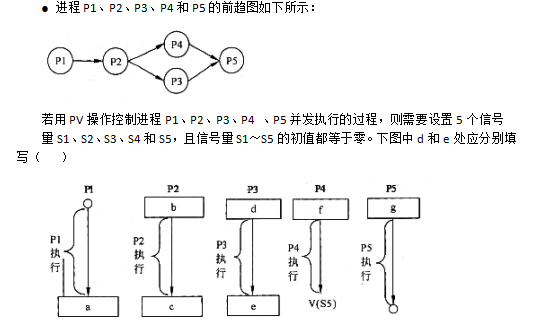

- A.V(S2)和P(S4)

- B.P(S2)和V(S4)

- C.P(S2)和P(S4)

- D.V(S2)和V(S4)

- 查看答案

-

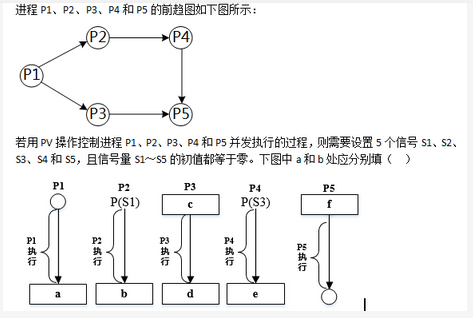

- A.V(S1)P(S2)和V(S3)

- B.P(S1)V(S2)和V(S3)

- C.V(S1)V(S2)和V(S3)

- D.P(S1)P(S2)和V(S3)

- 查看答案

-

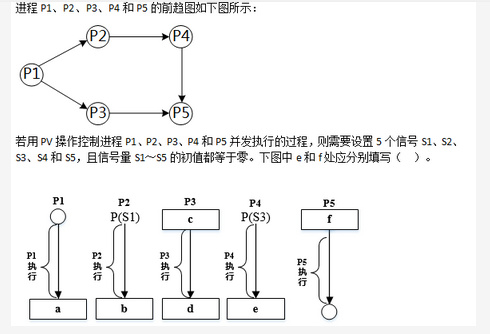

- A.P(S4)和V(S4)V(S5)

- B.V(S5)和P(S4)P(S5)

- C.V(S3)和V(S4)V(S5)

- D.P(S3)和P(S4)V(P5)

- 查看答案

-

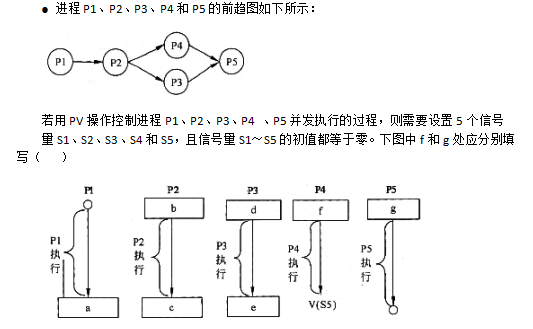

- A.P(S3)和V(S4)V(S5)

- B.V(S3)和P(S4)P(S5)

- C.P(S3)和P(S4)P(S5)

- D.V(S3)和V(S4)V(S5)

- 查看答案

-

- A.P(S2)和P(S4)

- B.P(S2)和V(S4)

- C.V(S2)和P(S4)

- D.V(S2)和V(S4)

- 查看答案