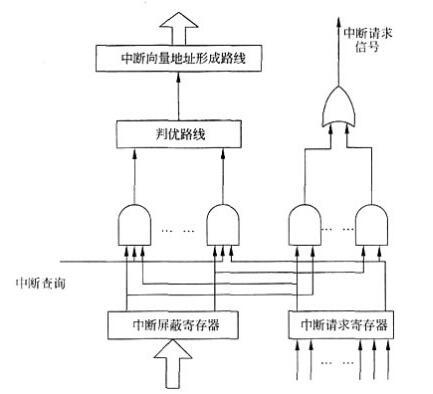

外部中断系统的基本结构如下图所示,由底层的中断请求到后续的CPU响应,关于该过程,以下描述中不正确的是______。

- A.中断请求会记录在中断请求寄存器的对应位

- B.中断屏蔽寄存器用来配置是否进行对应位的中断屏蔽

- C.从中断请求信号中即可判别出是哪个外部中断源产生的中断

- D.判优线路根据每个中断的优先级,选择一个最高优先级的中断源进行响应

正确答案及解析

正确答案

C

解析

本题考查嵌入式系统中断处理过程的基础知识。中断是指当出现需要时,CPU暂时停止当前程序的执行转而执行处理新情况的程序和执行过程。即在程序运行过程中,系统出现了一个必须由CPU立即处理的情况,此时,CPU暂时中止程序的执行转而处理这个新的情况的过程就叫做中断。中断的处理会涉及到底层硬件的响应机制和上层软件的处理方法。在中断控制器中,一般会包含有中断配置寄存器、中断状态寄存器、中断请求寄存器等。并且可能存在多个外设共用一个中断线的情况。对于CPU来说,一个系统中会存在多个中断的同时产生,因此需要在中断控制器中按照优先级逻辑进行中断选择,通知CPU进行中断处理。在其处理过程中,中断请求会记录在中断请求寄存器的对应位,中断屏蔽寄存器用来配置是否进行对应位的中断屏蔽,通过控制其值来进行使能或者关闭的控制。判优线路根据每个中断的优先级,选择一个最高优先级的中断源进行响应。由于有可能是多个外部中断源共用一个中断线,因此,当中断产生时,需要借助状态寄存器来判定是哪个中断源产生的对应中断。

包含此试题的试卷

你可能感兴趣的试题

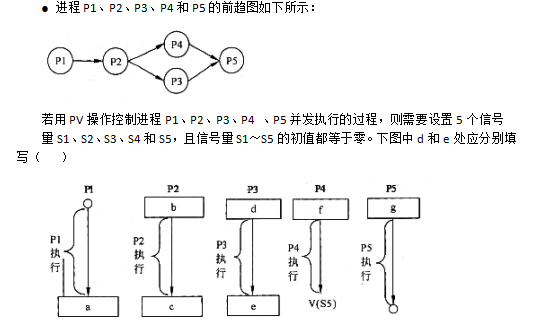

-

- A.V(S2)和P(S4)

- B.P(S2)和V(S4)

- C.P(S2)和P(S4)

- D.V(S2)和V(S4)

- 查看答案

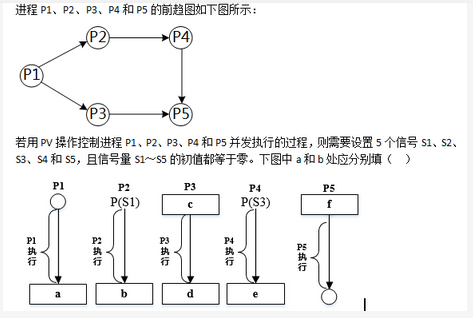

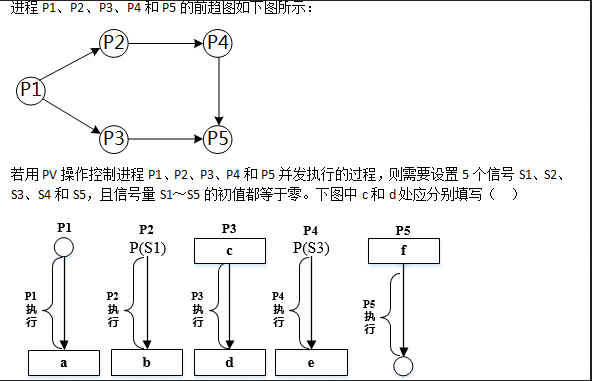

-

- A.V(S1)P(S2)和V(S3)

- B.P(S1)V(S2)和V(S3)

- C.V(S1)V(S2)和V(S3)

- D.P(S1)P(S2)和V(S3)

- 查看答案

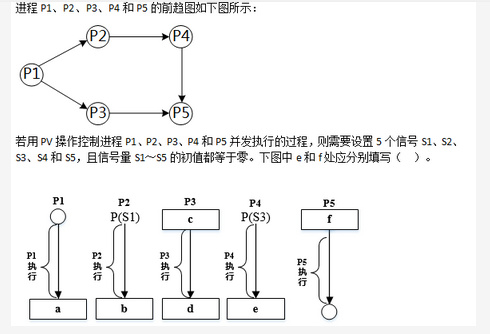

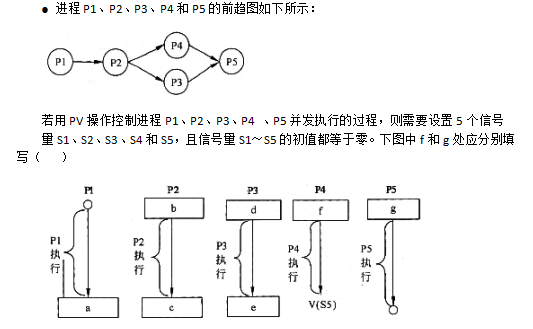

-

- A.P(S4)和V(S4)V(S5)

- B.V(S5)和P(S4)P(S5)

- C.V(S3)和V(S4)V(S5)

- D.P(S3)和P(S4)V(P5)

- 查看答案

-

- A.P(S3)和V(S4)V(S5)

- B.V(S3)和P(S4)P(S5)

- C.P(S3)和P(S4)P(S5)

- D.V(S3)和V(S4)V(S5)

- 查看答案

-

- A.P(S2)和P(S4)

- B.P(S2)和V(S4)

- C.V(S2)和P(S4)

- D.V(S2)和V(S4)

- 查看答案