在进行嵌入式系统硬件电路设计时,可采用()增强电路的抗干扰能刀。

- A.布线时走90度折线

- B.使用1C插座

- C.布线时减少回路环的面积

- D.闲置未用的I/O口尽量悬空

正确答案及解析

正确答案

C

解析

在进行嵌入式系统硬件电路设计时,提高敏感器件的抗干扰能力是指从敏感器件这边考虑尽量减少对干扰噪声的拾取以及从不正常状态尽快恢复。提高抗干扰能力的常用措施有:布线时尽量减少回路环的面积,以降低感应噪声;减少回路环面积布线时,电源线和地线要尽量粗;布线时避免90度折线,减少高频噪声发射;对于闲置未用的管脚不要悬空,在不改变系统逻辑的情况下接地或接电源;在速度能满足要求的前提下,尽量降低晶振频率和选用低速数字电路;器件尽量直接焊在电路板上,少用IC插座。

包含此试题的试卷

你可能感兴趣的试题

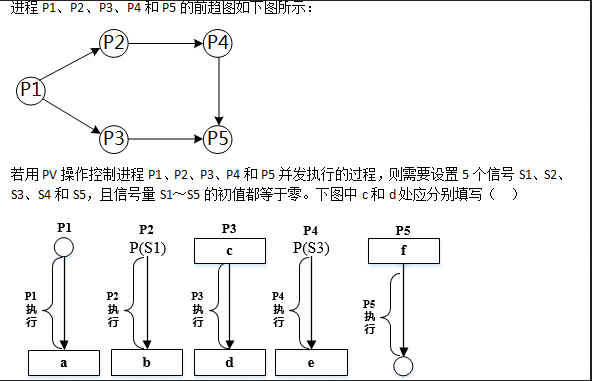

-

- A.V(S2)和P(S4)

- B.P(S2)和V(S4)

- C.P(S2)和P(S4)

- D.V(S2)和V(S4)

- 查看答案

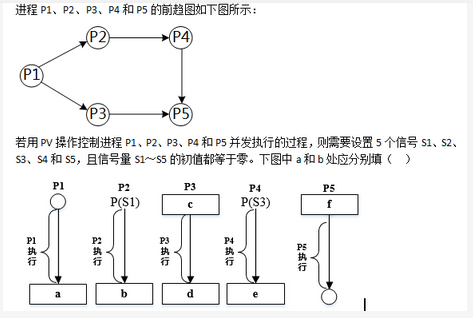

-

- A.V(S1)P(S2)和V(S3)

- B.P(S1)V(S2)和V(S3)

- C.V(S1)V(S2)和V(S3)

- D.P(S1)P(S2)和V(S3)

- 查看答案

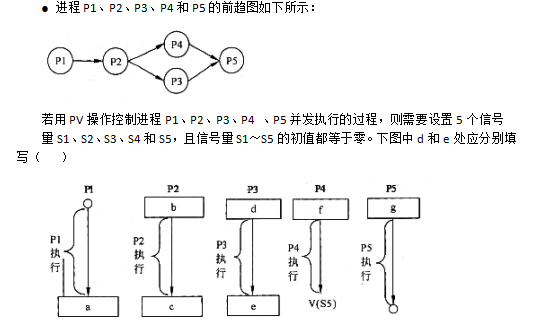

-

- A.P(S4)和V(S4)V(S5)

- B.V(S5)和P(S4)P(S5)

- C.V(S3)和V(S4)V(S5)

- D.P(S3)和P(S4)V(P5)

- 查看答案

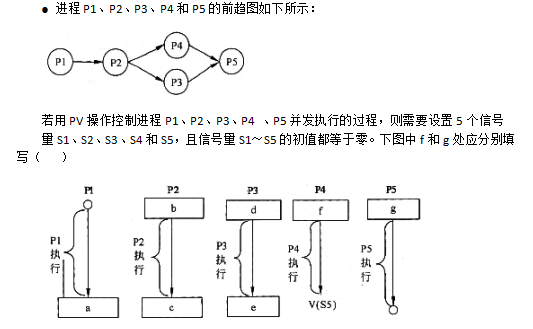

-

- A.P(S3)和V(S4)V(S5)

- B.V(S3)和P(S4)P(S5)

- C.P(S3)和P(S4)P(S5)

- D.V(S3)和V(S4)V(S5)

- 查看答案

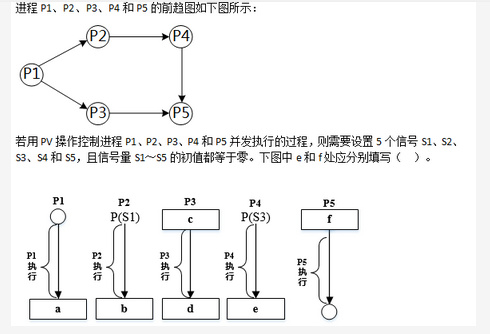

-

- A.P(S2)和P(S4)

- B.P(S2)和V(S4)

- C.V(S2)和P(S4)

- D.V(S2)和V(S4)

- 查看答案