以下关于 Cache ( 高速缓冲存储器 ) 的叙述中,不正确的是( )

- A.Cache的设置扩大了主存的容量

- B.Cache的内容是主存部分内容的拷贝

- C.Cache的命中率并不随其容量增大线性地提高

- D.Cache位于主存与CPU之间

正确答案及解析

正确答案

A

解析

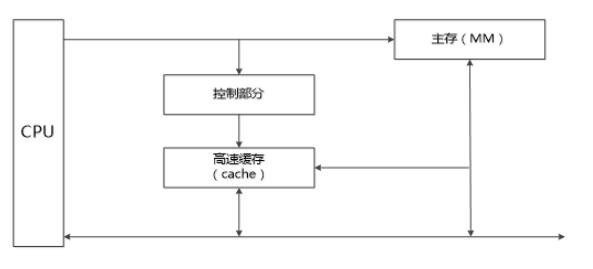

高速缓存是用来存放当前最活跃的程序和数据的,作为主存局部域的副本,其特点是:容量一般在几KB到几MB之间;速度一般比主存快5到10倍,由快速半导体存储器构成;其内容是主存局部域的副本,对程序员来说是透明的。高速缓存的组成如下图所示:Cache由两部分组成:控制部分和cache部分。Cache部分用来存放主存的部分拷贝(副本)信息。控制部分的功能是:判断CPU要访问的信息是否在cache中,若在即为命中,若不在则没有命中。命中时直接对cache存储器寻址。未命中时,要按照替换原则,决定主存的一块信息放到cache的哪一块里面。

你可能感兴趣的试题

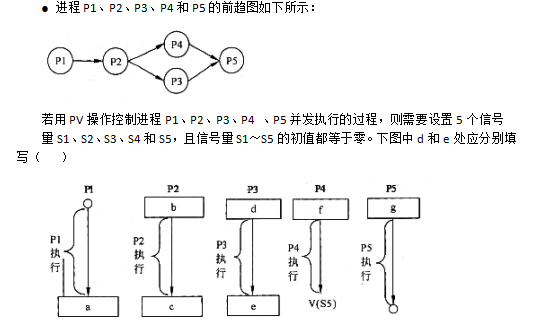

-

- A.V(S2)和P(S4)

- B.P(S2)和V(S4)

- C.P(S2)和P(S4)

- D.V(S2)和V(S4)

- 查看答案

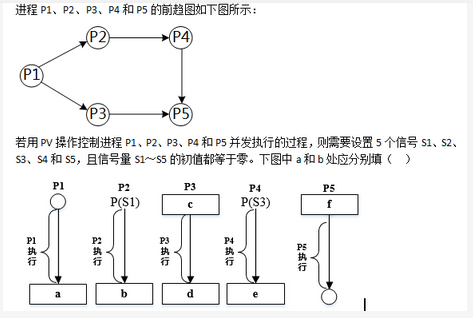

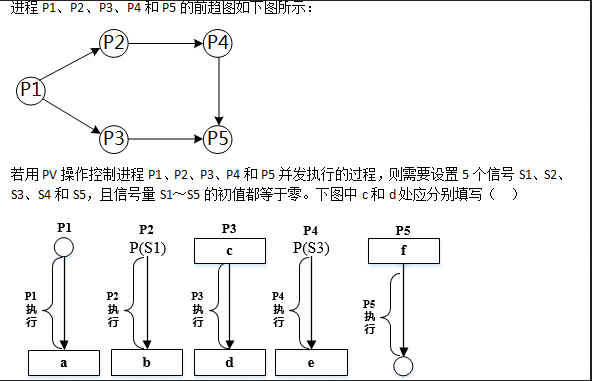

-

- A.V(S1)P(S2)和V(S3)

- B.P(S1)V(S2)和V(S3)

- C.V(S1)V(S2)和V(S3)

- D.P(S1)P(S2)和V(S3)

- 查看答案

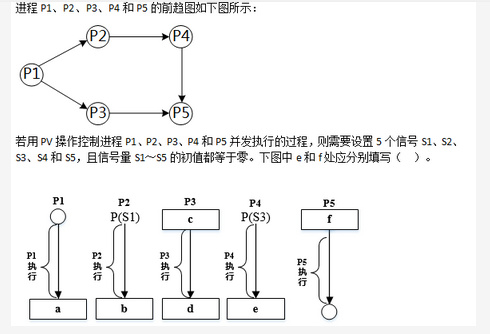

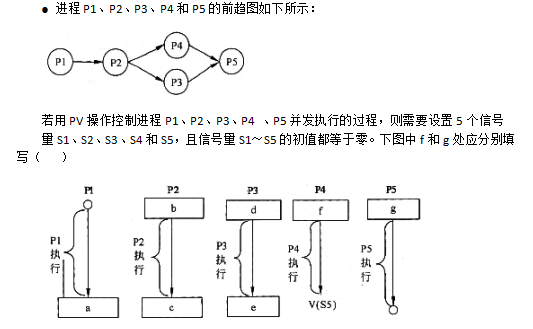

-

- A.P(S4)和V(S4)V(S5)

- B.V(S5)和P(S4)P(S5)

- C.V(S3)和V(S4)V(S5)

- D.P(S3)和P(S4)V(P5)

- 查看答案

-

- A.P(S3)和V(S4)V(S5)

- B.V(S3)和P(S4)P(S5)

- C.P(S3)和P(S4)P(S5)

- D.V(S3)和V(S4)V(S5)

- 查看答案

-

- A.P(S2)和P(S4)

- B.P(S2)和V(S4)

- C.V(S2)和P(S4)

- D.V(S2)和V(S4)

- 查看答案